# VAX-11/730 Central Processing Unit Technical Description

# Copyright © 1982 by Digital Equipment Corporation

#### All Rights Reserved

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

This document was set on DIGITAL's DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DIGITAL      | DECsystem-10     | MASSBUS |

|--------------|------------------|---------|

| DEC          | DECSYSTEM-20     | OMNIBUS |

| PDP          | DIBOL            | OS/8    |

| <b>DECUS</b> | <b>EDUSYSTEM</b> | RSTS    |

| UNIBUS       | VAX              | RSX     |

|              | VMS              | IAS     |

# **CONTENTS**

| CHAPTER 1 | INTRODUCTION AND SYSTEM OVERVIEW                  |                |

|-----------|---------------------------------------------------|----------------|

| 1.1       | MANUAL SCOPE AND RELATED DOCUMENTS                | 1-1            |

| 1.2       | INTRODUCTION TO THE VAX-11/730                    | 1-2            |

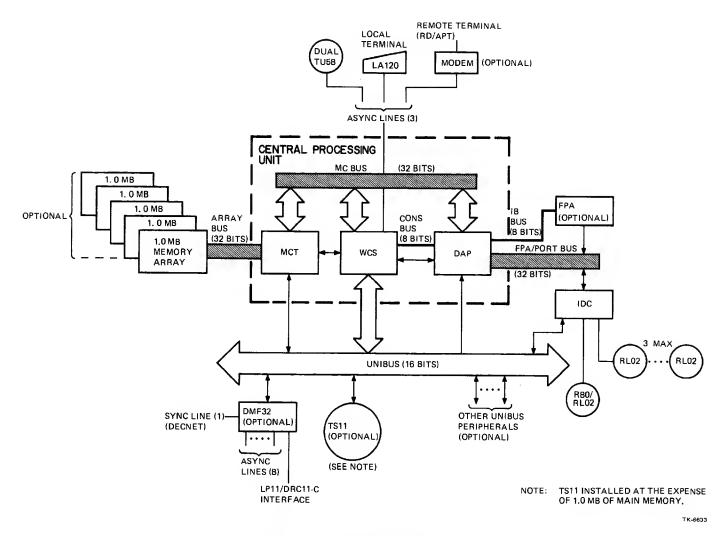

| 1.3       | VAX-11/730 SYSTEM CONFIGURATION                   | 1-2            |

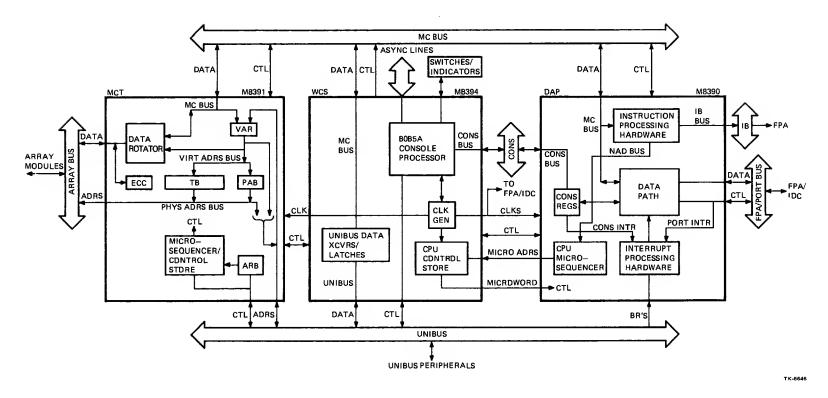

| 1.3.1     | KA730 Central Processing Unit (CPU)               | 1-4            |

| 1.3.2     | Main Memory Array                                 | 1-6            |

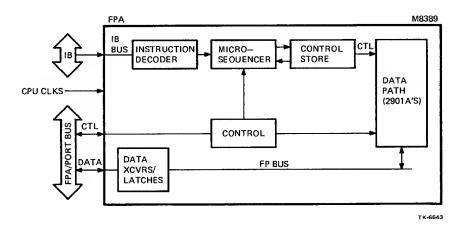

| 1.3.3     | FP730 Floating-Point Accelerator (FPA)            | 1-6            |

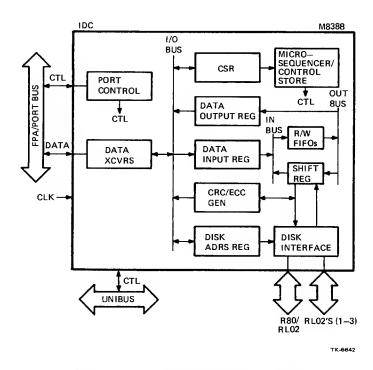

| 1.3.4     | RB730 Integrated Disk Controller (IDC)            | 1-7            |

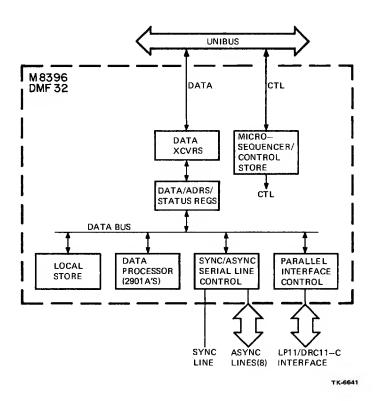

| 1.3.5     | DMF32                                             | 1-8            |

| 1.4       | SYSTEM ARCHITECTURE                               | 1-9            |

| 1.5       | SWITCHES AND INDICATORS                           | 1-9            |

| 1.6       | CONSOLE COMMANDS/BASIC OPERATOR CONTROL           | 1-9            |

| 1.7       | DIAGNOSTIC AND MAINTENANCE AIDS                   | 1-9            |

| 1.8       | PHYSICAL DESCRIPTION                              | 1-10           |

| 1.9       | SYSTEM TIMING                                     | 1-10           |

| 1.10      | SYSTEM BUS SUMMARY                                | 1-11           |

| 1.10.1    | UNIBUS                                            | 1-12           |

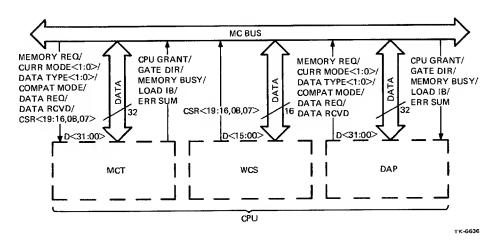

| 1.10.2    | Memory Control (MC) Bus                           | 1-14           |

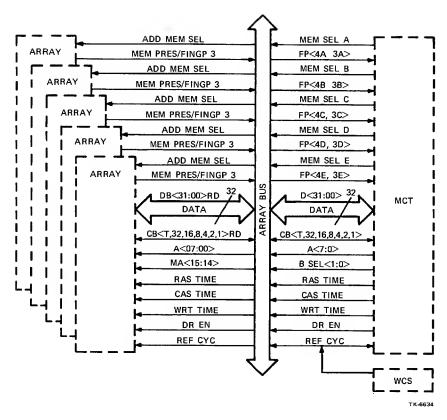

| 1.10.3    | Memory Array Bus                                  | 1-16           |

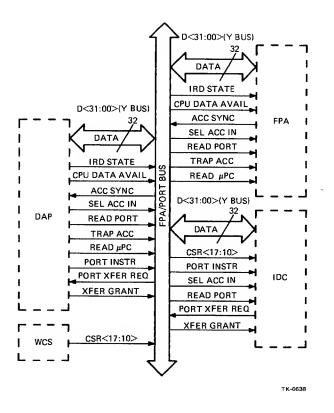

| 1.10.4    | FPA/Port Bus                                      | 1-19           |

| 1.10.5    | Console Bus                                       | 1-21           |

| 1.10.6    | IB Bus                                            | 1-21           |

| 1.11      | DEFINITION OF THE CPU FOR DOCUMENTATION PURPOSES  |                |

| ****      |                                                   |                |

| CHAPTER 2 | CONSOLE PROCESSOR                                 |                |

| 2.1       | INTRODUCTION                                      | 2-1            |

| 2.2       | 8085A MICROPROCESSOR                              | 2-5            |

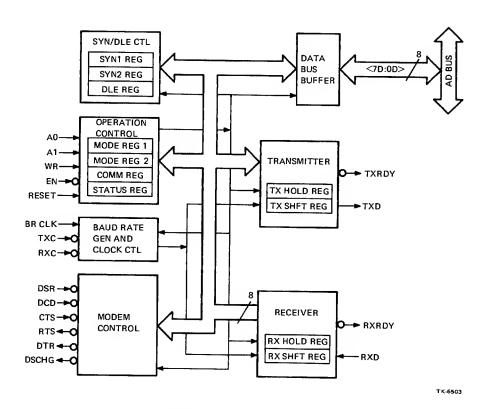

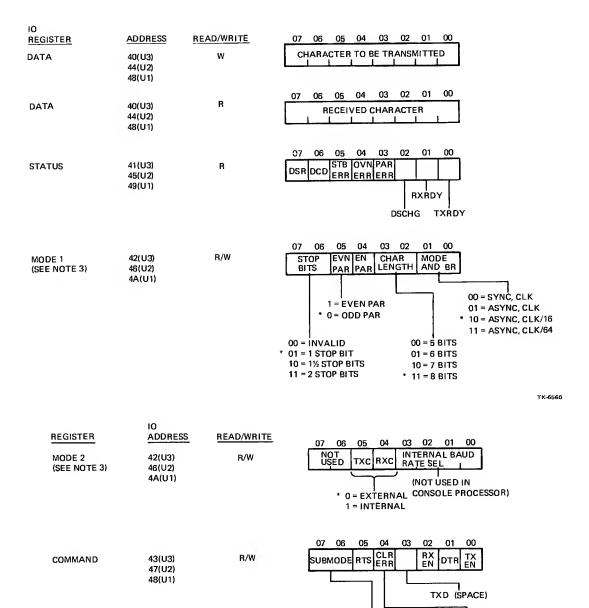

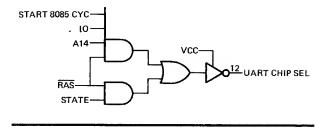

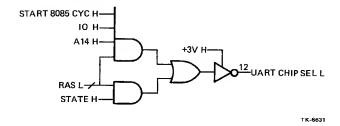

| 2.3       | 2651 USARTS                                       | 2-9            |

| 2.3.1     | Basic Operations                                  | 2-11           |

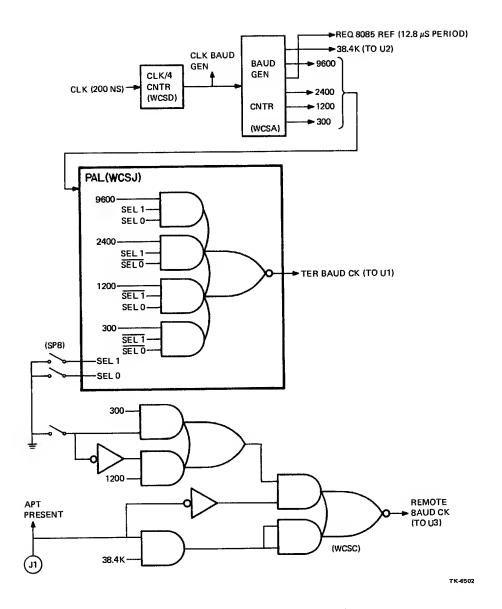

| 2.3.2     | USART Clocks                                      |                |

| 2.3.3     | Terminal and Tape Data Transfers.                 |                |

| 2.4       | THE 9513 INTERVAL TIMER.                          | 2-18           |

| 2.4.1     | 9513 Register Addressing                          |                |

| 2.4.2     | 95 13 Control Registers                           | 2-24           |

| 2.4.3     | CPU Interval Timer (Counter Logic Groups 1 and 2) |                |

| 2.4.4     | Time of Year Clock (Counter Logic Groups 4 and 5) |                |

| 2.4.5     | Power Fail Timer (Counter Logic Group 3)          | 2-31           |

| 2.4.3     | CONSOLE READ/WRITE OPERATIONS                     | 2-32           |

| 2.5.1     | Read/Write Control Logic                          | 2-33           |

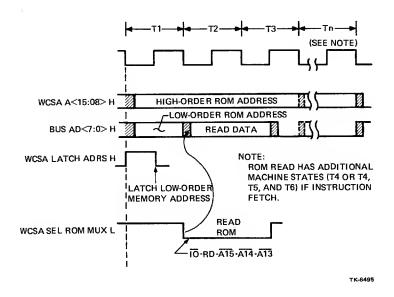

| 2.5.2     | ROM Operations                                    | 2-36           |

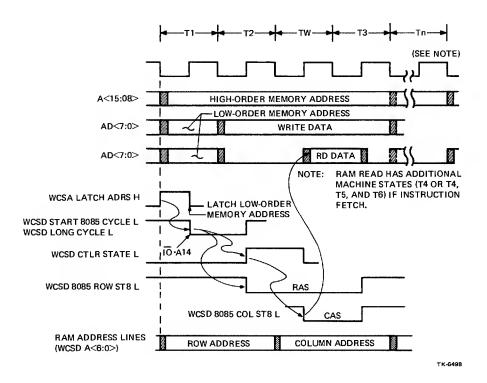

| 2.5.3     | RAM Operations                                    | 2-37           |

| ۷.۶.۶     | term operations                                   | <del>-</del> 9 |

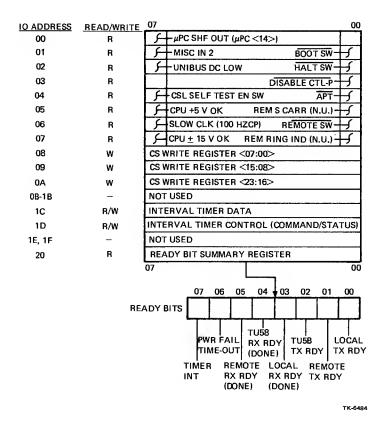

| 2.5.4     | I/O Operations                               |

|-----------|----------------------------------------------|

| 2.5.4.1   | Reading and Writing the USART Registers      |

| 2.5.4.2   | Reading and Writing the Other I/O Devices    |

| 2.6       | COMMUNICATIONS BETWEEN CONSOLE PROCESSOR AND |

| _,,       | DATA PATH                                    |

| 2.6.1     | Communications in Console Mode               |

| 2.6.2     | Communications in Program Mode               |

| 2.0.2     | Communications in Frogram Mode               |

| CHAPTER 3 | CPU CLOCK GENERATOR                          |

| 3.1       | INTRODUCTION                                 |

| 3.2       | CLOCK GENERATOR CIRCUIT                      |

| 3.3       | CLOCK START/STOP/STEP CONTROL                |

| 3.3.1     | Clock Controls by the Console                |

| 3.3.2     | Clock Stalls                                 |

| J.J.2     | CIOCK Dialis                                 |

| CHAPTER 4 | CPU CONTROL STORE AND MICROSEQUENCER         |

| 4.1       | INTRODUCTION4-1                              |

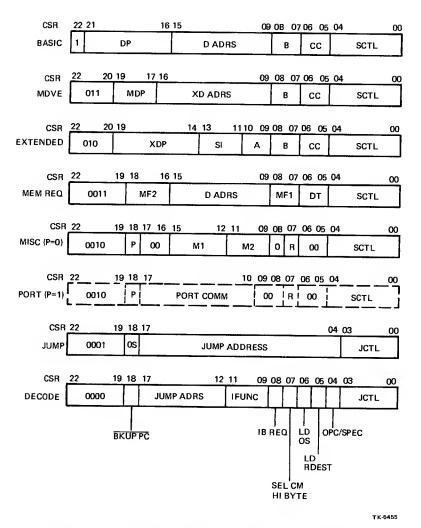

| 4.2       | MICROINSTRUCTION FORMATS                     |

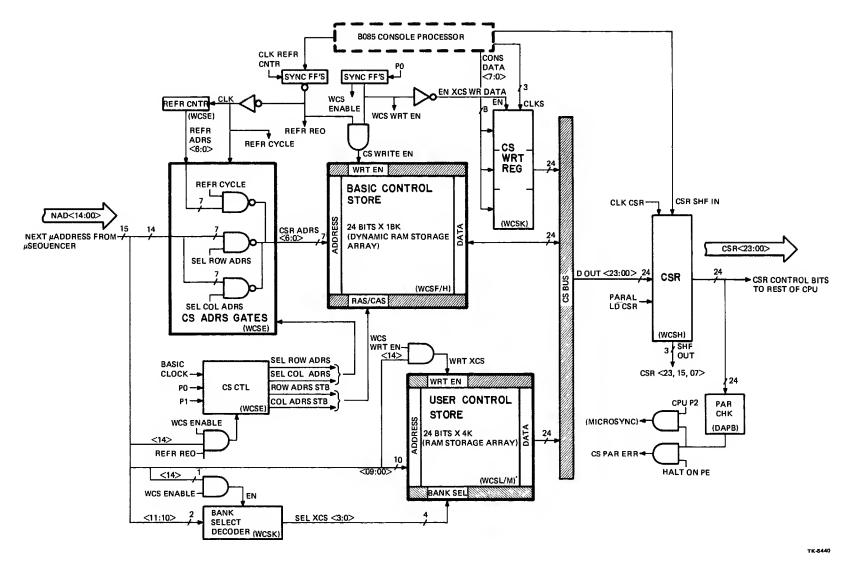

| 4.3       | CONTROL STORE. 4-9                           |

| 4.3.1     | Basic Control Store Storage Array. 4-11      |

| 4.3.2     | User Control Store Storage Array             |

| 4.3.3     | Control Store Perister (CSP)                 |

| 4.3.4     | Control Store Register (CSR)                 |

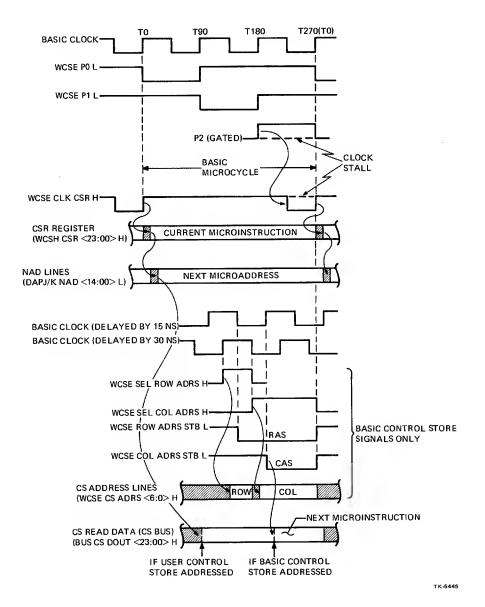

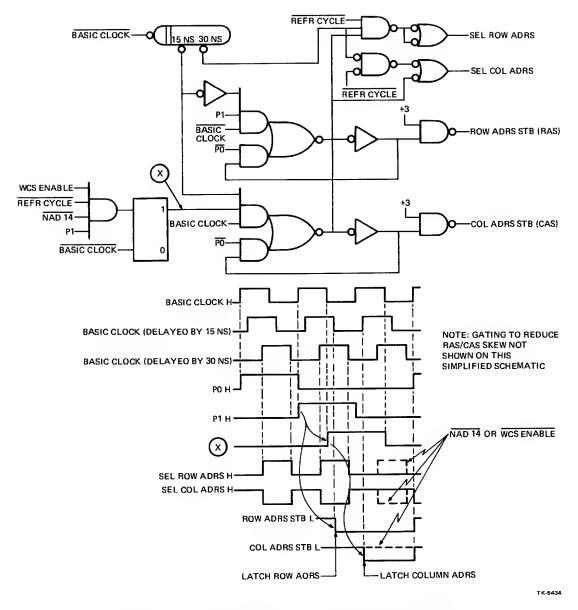

| 4.3.5     | Basic Microcycle                             |

| 4.3.6     | Control Store Refresh Cycle                  |

|           | Control Store Write Operation                |

| 4.3.7     | Control Store Parity and Microsync           |

| 4.4       | MICROSEQUENCER                               |

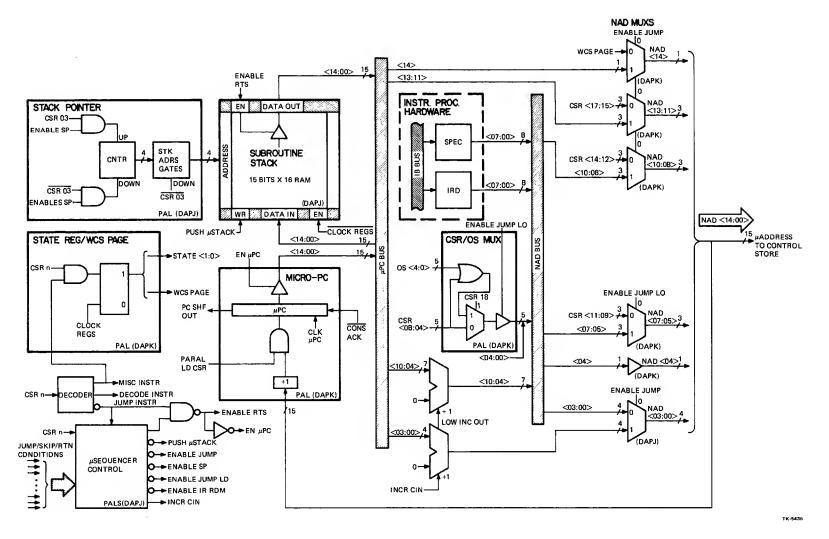

| 4.4.1     | Micro-PC4-19                                 |

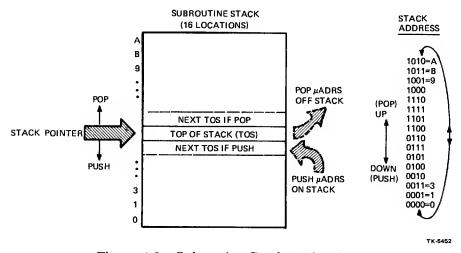

| 4.4.2     | Subroutine Stack                             |

| 4.4.3     | State Register                               |

| 4.4.4     | Microsequencer Control4-22                   |

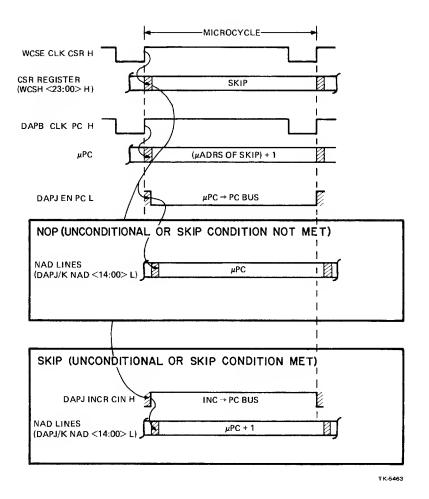

| 4.4.5     | Skip (Or No-Skip) Operations                 |

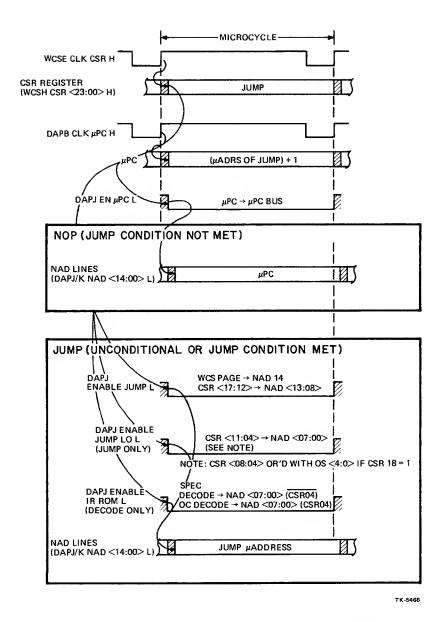

| 4.4.6     | Jump (Or No-Jump) Operations                 |

| 4.4.7     | Subroutine Jumps and Returns4-28             |

| 4.4.8     | Iteration Control (Loops and Pops)           |

| CHAPTER 5 | INSTRUCTION PROCESSING HARDWARE              |

| 5.1       | INTRODUCTION                                 |

| 5.2       | INSTRUCTION PREFETCH REGISTER (PFR). 5-3     |

| 5.2.1     | Loading and PFR                              |

| 5.2.1.1   | Instruction Data in the PFR                  |

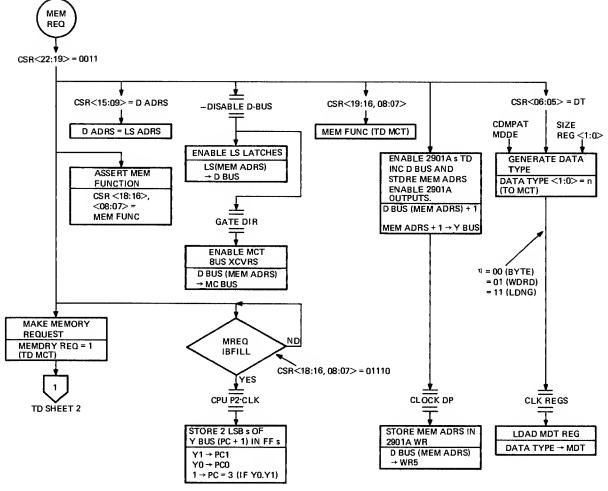

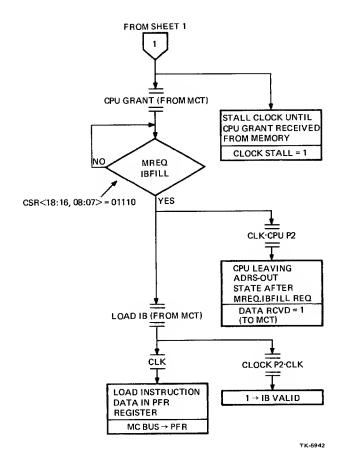

| 5.2.1.2   | Detailed Operation for the PFR Load          |

| 5.2.2     | Unloading the PFR 5.7                        |

|           |                                              |

| 5.3        | OPCODE REGISTER (OPC)5-9                    |

|------------|---------------------------------------------|

| 5.4        | MAPPING ROMS                                |

| 5.5        | REGISTER DESTINATION (GPR DEST) CONTROL BIT |

|            |                                             |

| 5.6        | REGISTER BACKUP MASK FLAG                   |

| 5.7        | INSTRUCTION DECODE OPERATIONS               |

| 5.7.1      | Class Decodes                               |

| 5.7.2      | Specifier Decodes                           |

| 5.7.3      | Other Decode Operations                     |

|            |                                             |

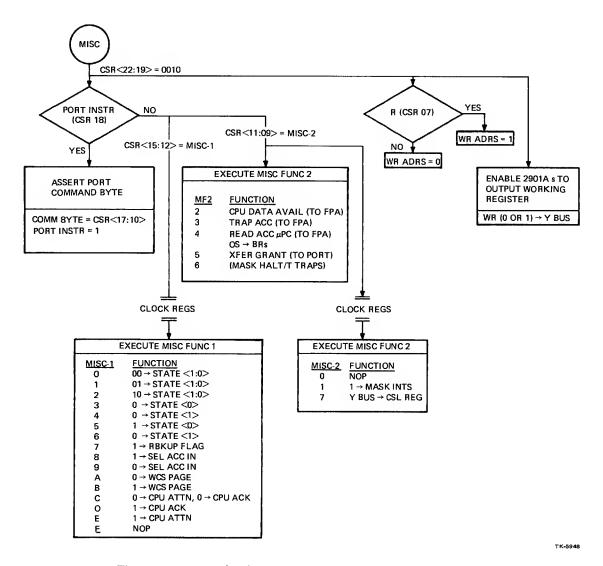

| CHAPTER 6  | DATA PATH                                   |

| CHAITERO   | DAIA AIII                                   |

| 6.1        | INTRODUCTION                                |

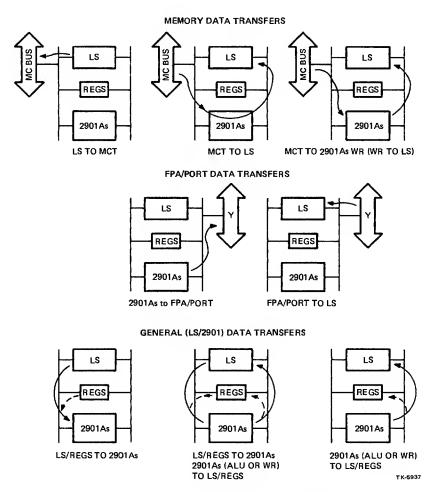

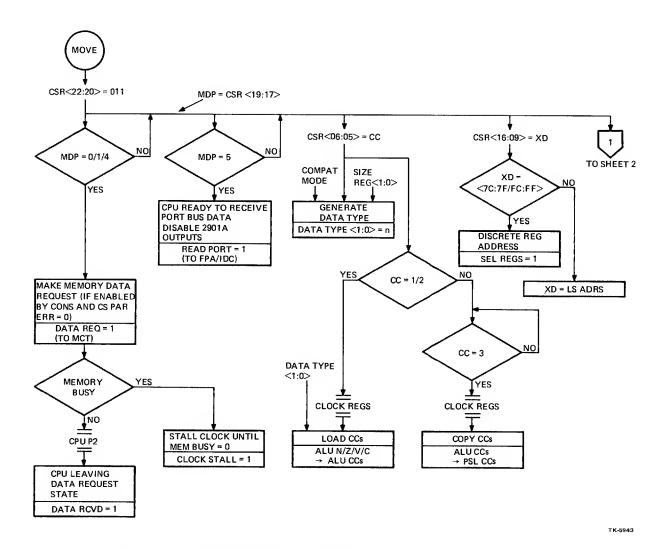

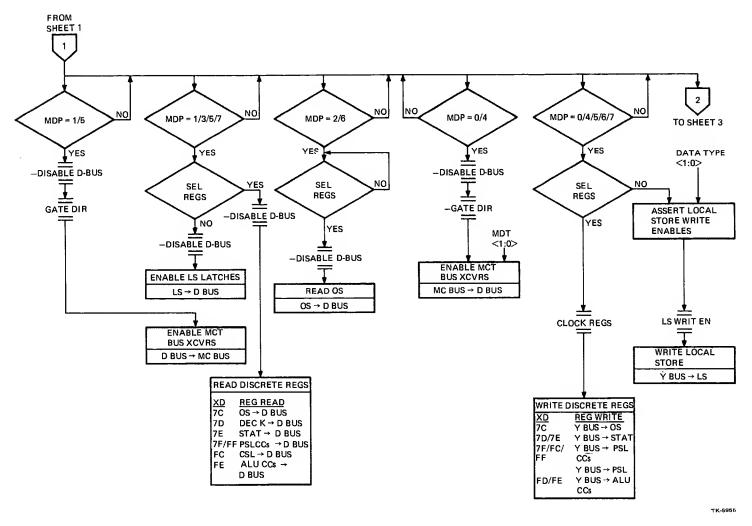

| 6.2        | BASIC DATA PATH TRANSFERS6-3                |

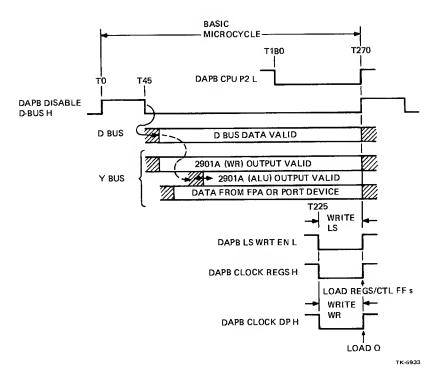

| 6.3        | BASIC DATA PATH TIMING                      |

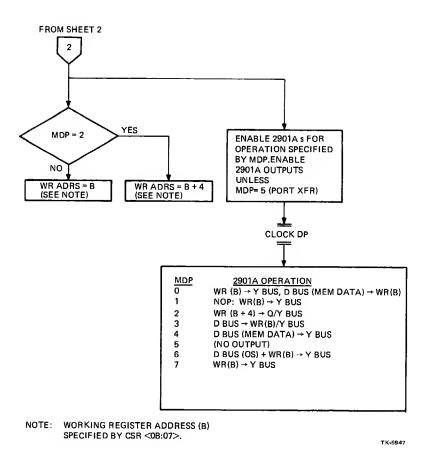

| 6.4        | 2901A DATA PROCESSOR                        |

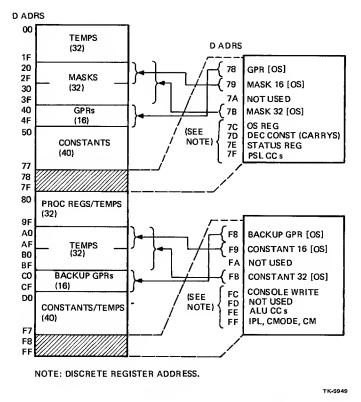

| 6.4.1      | 2901A RAM (Working Register) Addressing 6-9 |

| 6.4.2      | 2901A Control Bit Generation                |

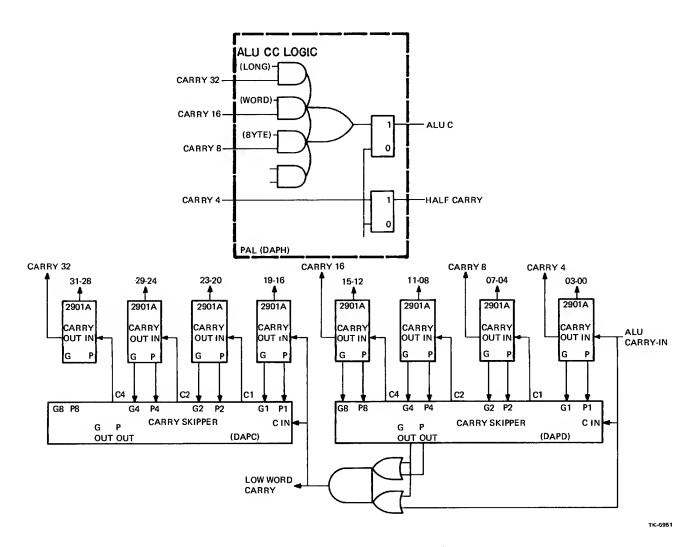

| 6.4.3      | Carry Logic                                 |

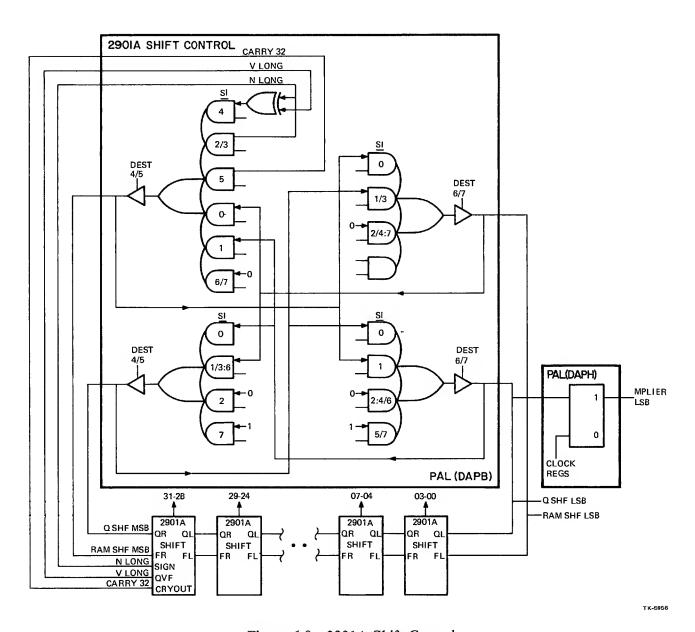

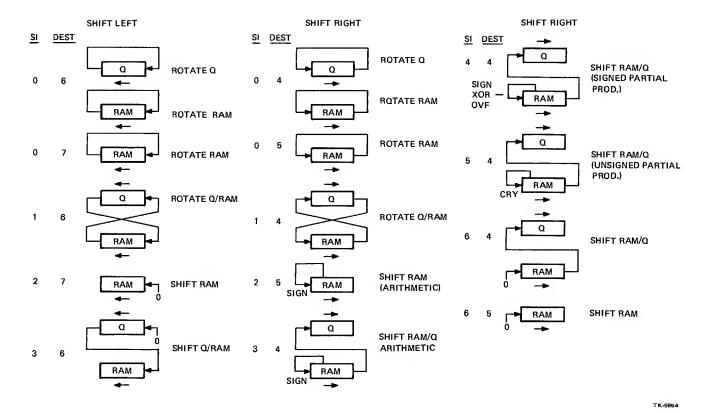

| 6.4.4      | Shift Control                               |

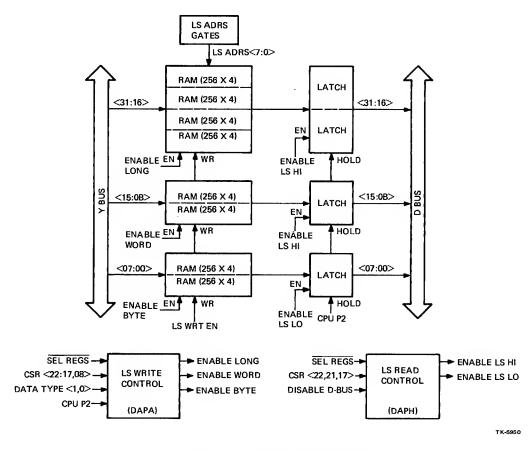

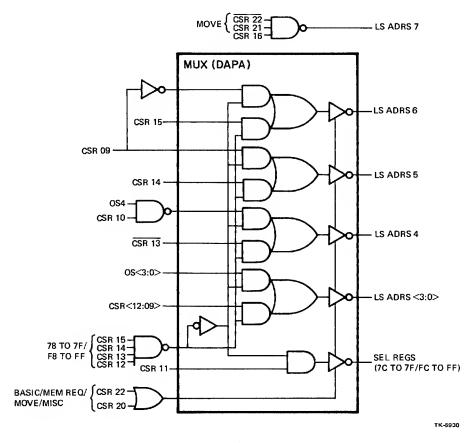

| 6.5        | LOCAL STORE (LS)                            |

| 6.6        | OPERAND SPECIFIER (OS) REGISTER             |

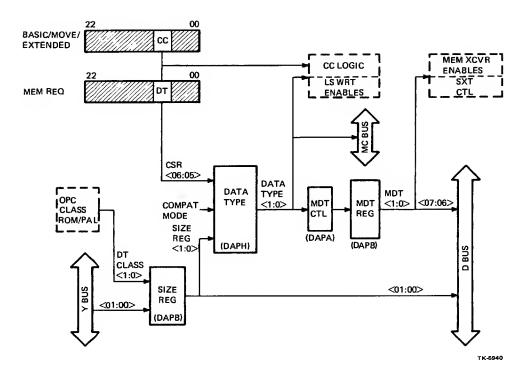

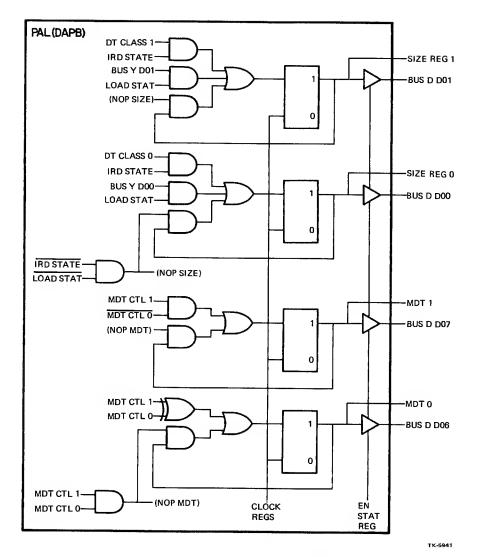

| 6.7        | DATA TYPE CONTROL                           |

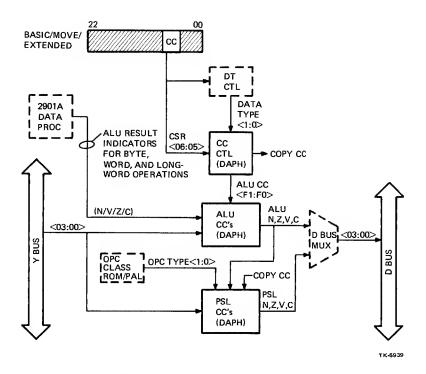

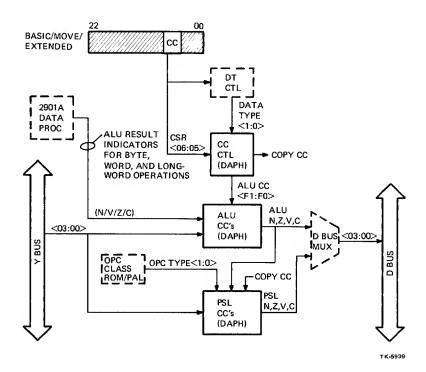

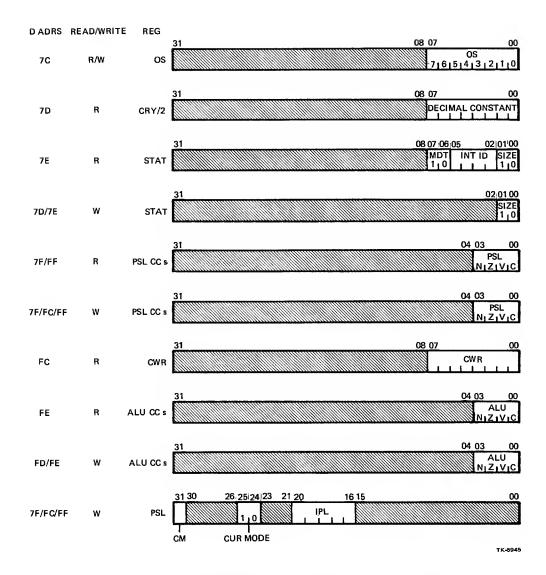

| 6.8        | CONDITION CODE (CC) LOGIC                   |

|            | · · ·                                       |

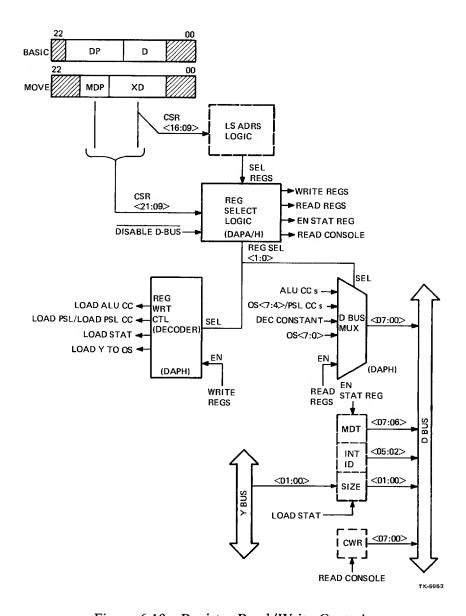

| 6.9        | REGISTER READ/WRITE CONTROL                 |

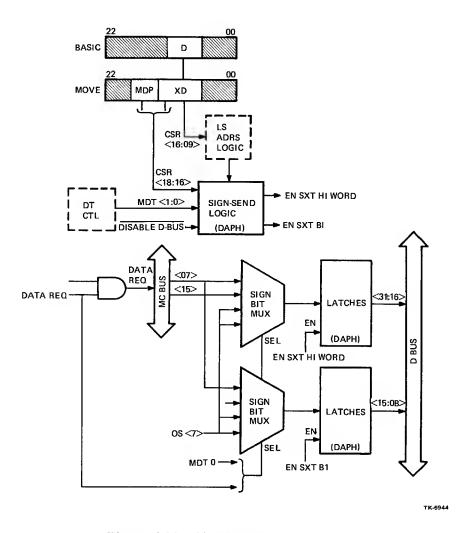

| 6.10       | SIGN EXTENSION CONTROL                      |

| 6.11       | MEMORY REFERENCES                           |

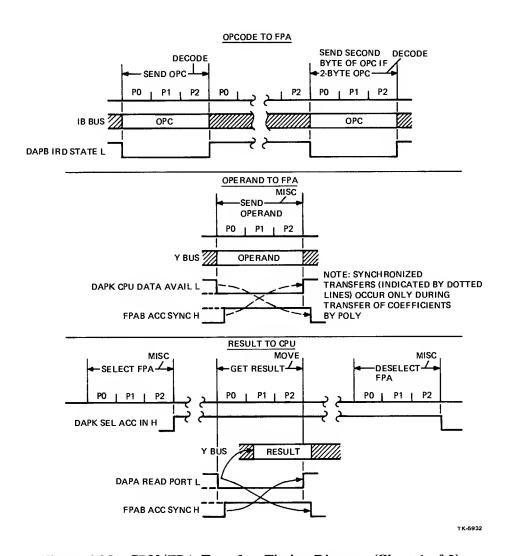

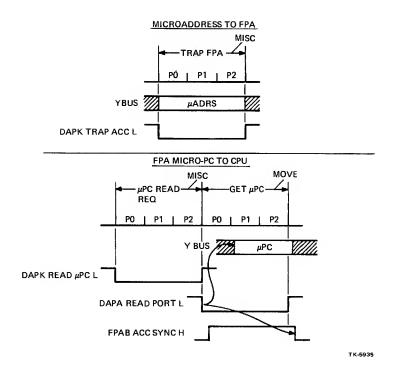

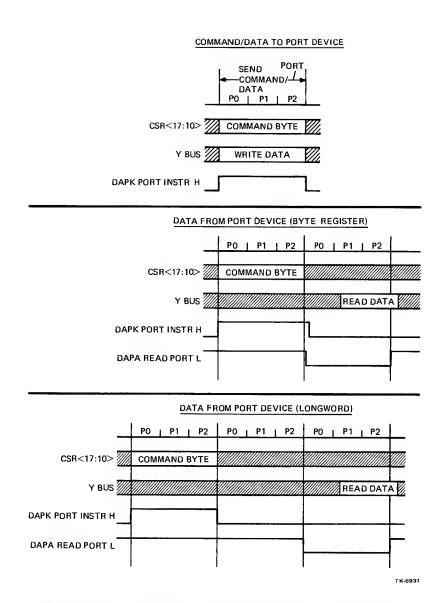

| 6.12       | FPA/PORT DEVICE TRANSFERS                   |

|            |                                             |

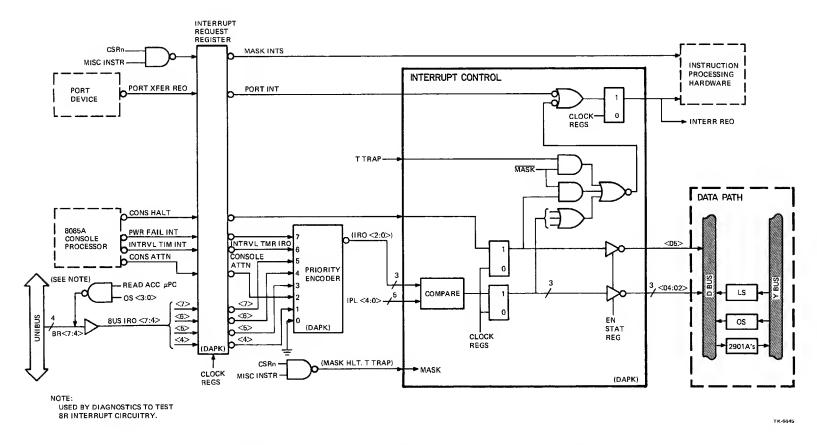

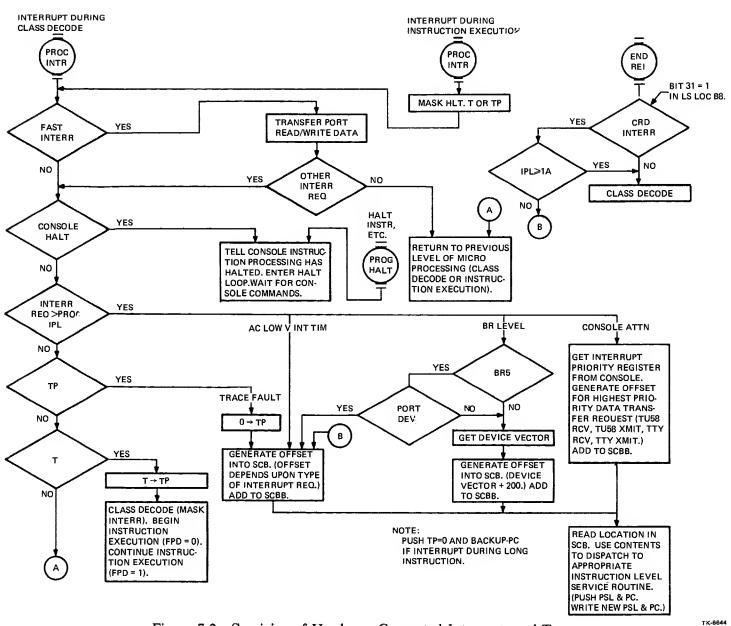

| CHAPTER 7  | INTERRUPT PROCESSING HARDWARE               |

|            |                                             |

| 7.1        | INTRODUCTION7-1                             |

| 7.2        | INTERRUPT DETECTION AND IDENTIFICATION      |

| 7.2.1      | Interrupt Request Register7-6               |

| 7.2.2      | Priority Encoder Circuit                    |

| 7.2.3      | Interrupt Control                           |

| 7.2.4      | Interrupt Priority                          |

| 7.2.5      | Interrupt Mask Functions                    |

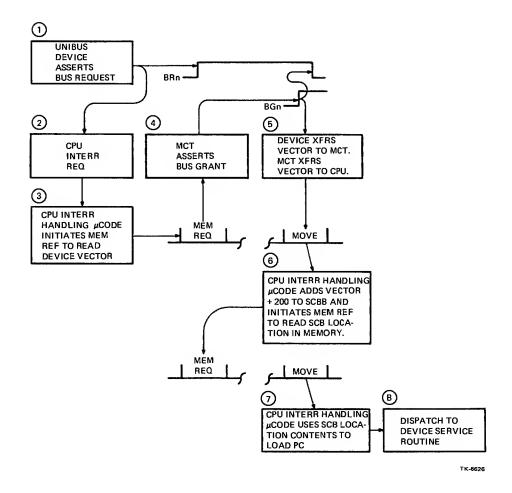

| 7.3        | UNIBUS INTERRUPTS                           |

| 7.4<br>7.4 | CONSOLE INTERRUPTS. 7-9                     |

| 7.5        | TRACING                                     |

| 7.6        | PORT (FAST) INTERRUPTS                      |

| 7.7        | PORT (SLOW) INTERRUPTS                      |

| 7.8        | CORRECTED MEMORY ERROR INTERRUPTS           |

| 7.0        |                                             |

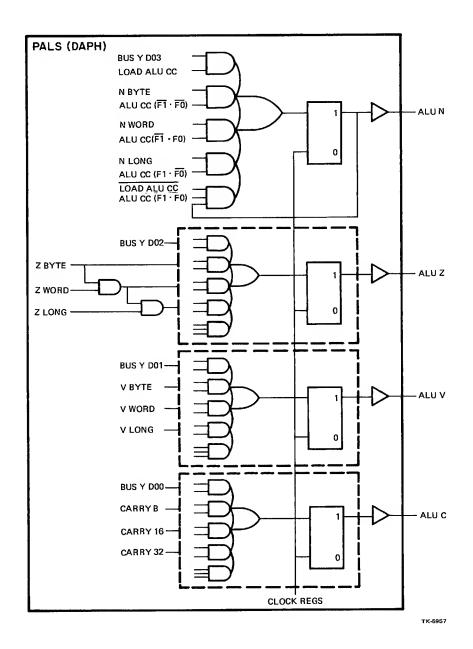

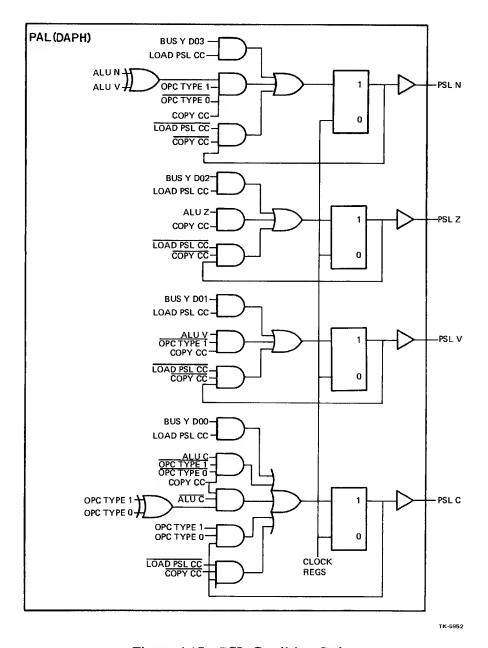

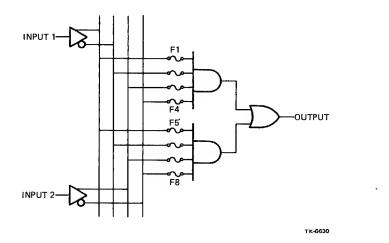

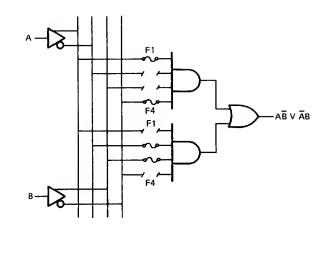

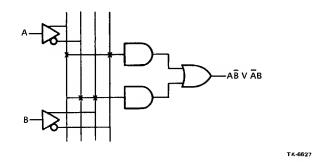

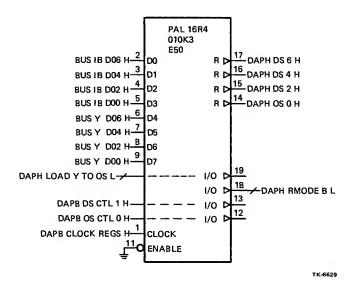

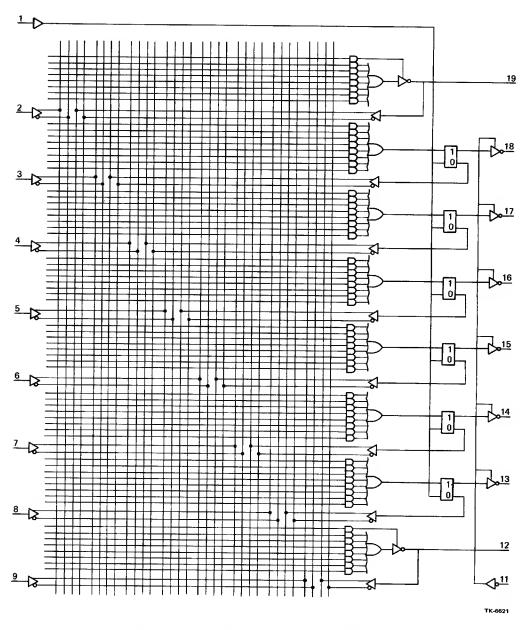

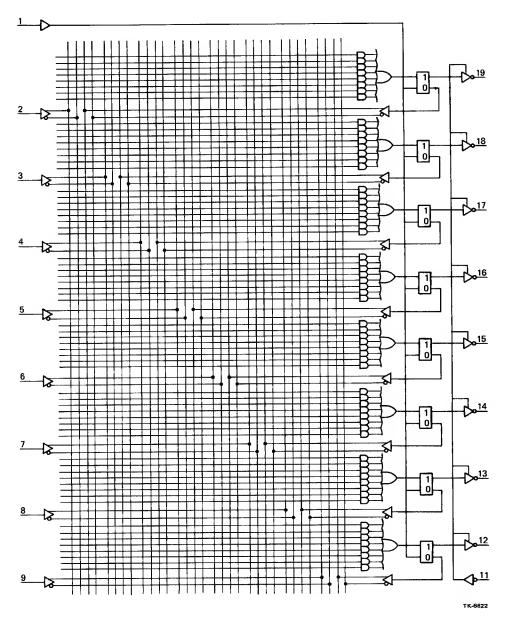

| APPENDIX A               | PROGRAMMED ARRAY LOGIC DEVICES (PALS)                                    |            |

|--------------------------|--------------------------------------------------------------------------|------------|

| A.1<br>A.2<br>A.3<br>A.4 | INTRODUCTION                                                             | A-2<br>A-3 |

| A.5                      | PAL LOGIC DIAGRAMS                                                       |            |

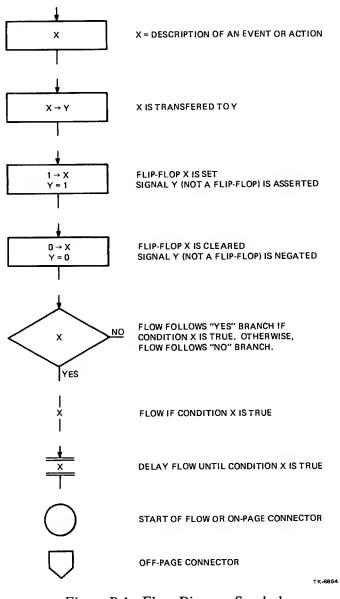

| APPENDIX B               | FLOW DIAGRAM SYMBOLS                                                     |            |

|                          | FIGURES                                                                  |            |

| Figure No.               | Title                                                                    | Page       |

| 1-1                      | VAX-11/730 System                                                        | 1-3        |

| 1-2                      | KA730 Block Diagram                                                      | 1-5        |

| 1-3                      | Floating-Point Accelerator                                               | 1-6        |

| 1-4                      | Integrated Disk Controller                                               |            |

| 1-5                      | DMF32                                                                    |            |

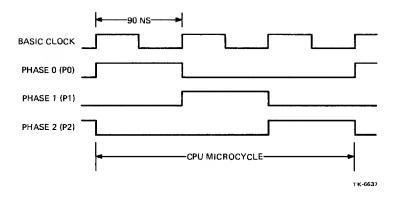

| 1-6                      | Basic System Clocks                                                      |            |

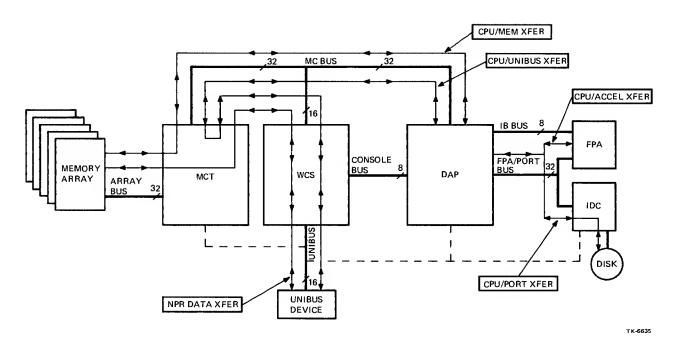

| 1-7                      | Major Bus Data Transfers, Data Flow                                      |            |

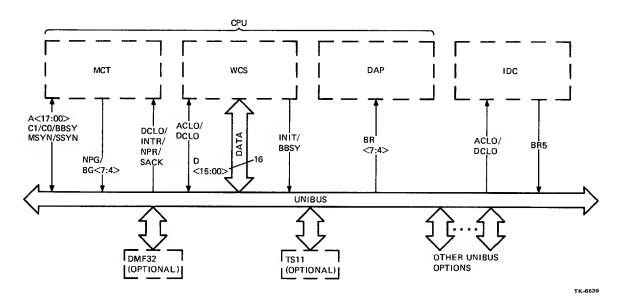

| 1-8                      | VAX-11/730 UNIBUS                                                        |            |

| 1-9                      | VAX-11/730 Memory Control (MC) Bus.                                      |            |

| 1-10                     | VAX-11/730 Memory Array Bus.                                             |            |

| 1-11                     | VAX-11/730 FPA/Port Bus.                                                 | . 1-19     |

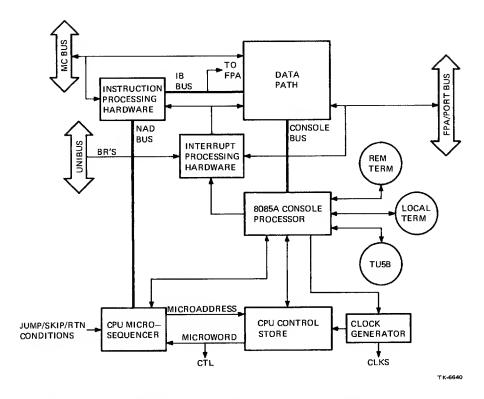

| 1-12                     | Central Processing Unit Functional Block Diagram                         | . 1-22     |

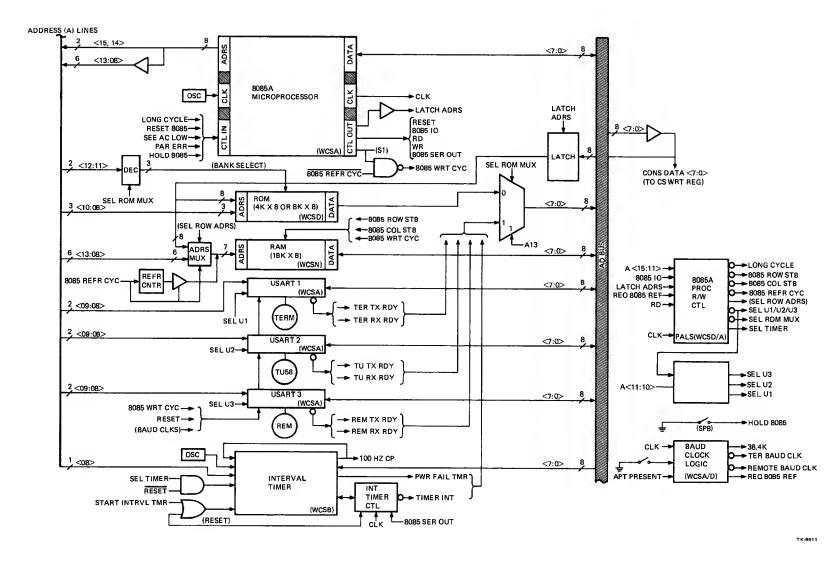

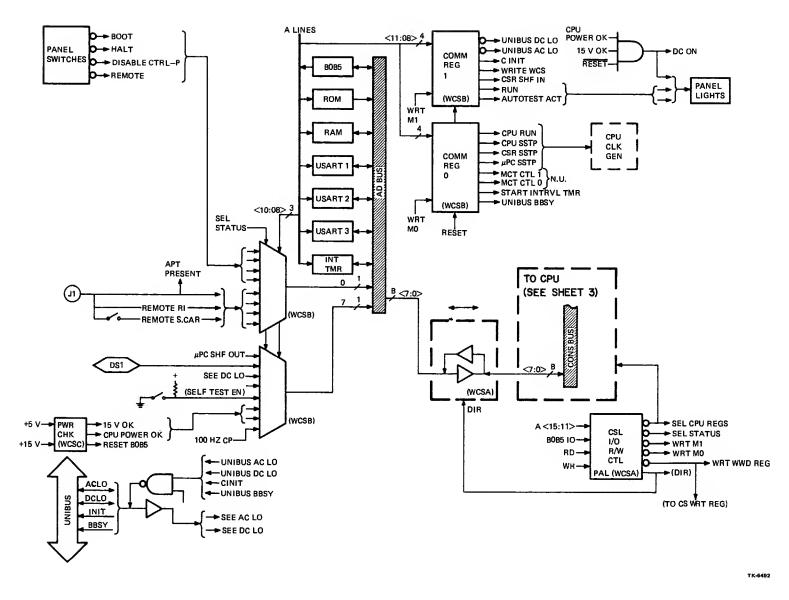

| 2-1                      | 8085A Console Processor                                                  |            |

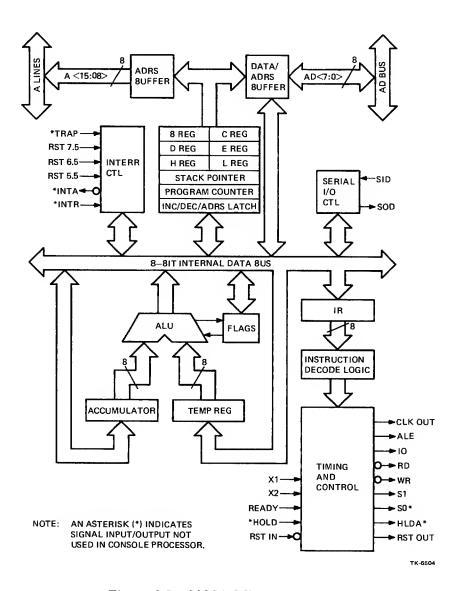

| 2-2                      | 8085A Microprocessor                                                     |            |

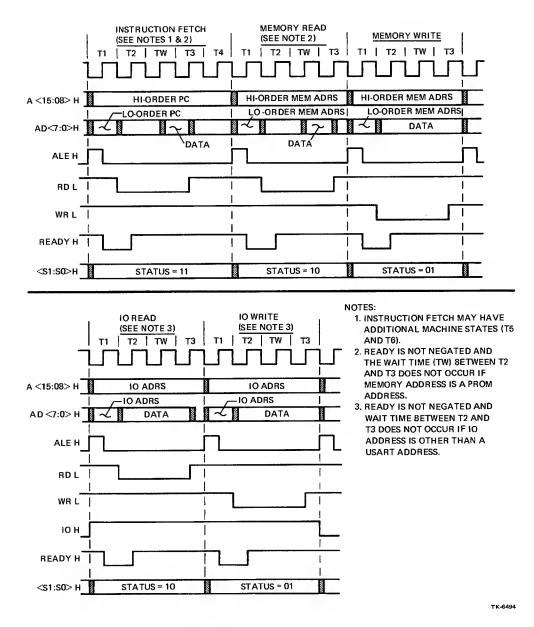

| 2-3                      | 8085A Machine Cycles Timing Diagram                                      |            |

| 2-4<br>2-5               | 2651 USART                                                               |            |

|                          | Bit Formats for 2651 USART Registers                                     |            |

| 2-6                      | Baud Clock Logic                                                         | . 2-14     |

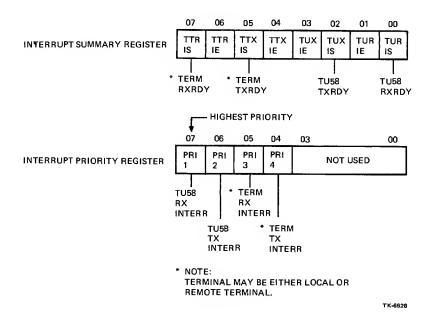

| 2-7                      | Bit Formats for Interrupt Summary and Priority Registers in Console      | 2.15       |

| 2-8                      | Program                                                                  |            |

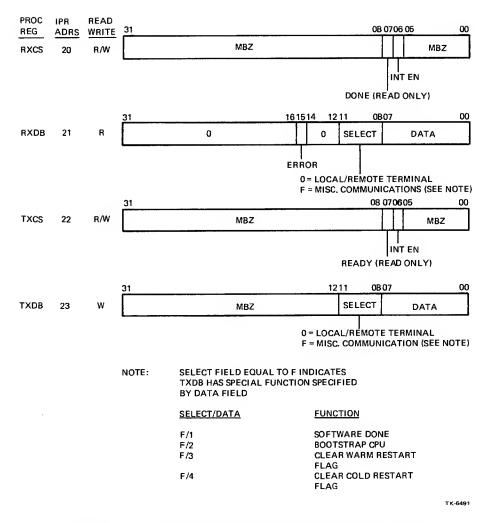

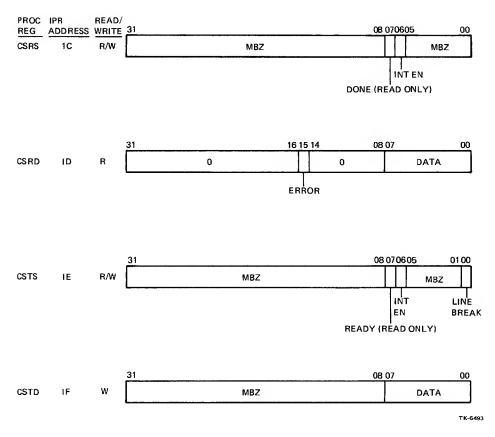

| 2-9                      | Bit Formats for Console Storage (Tape) Data and Control/Status Registers |            |

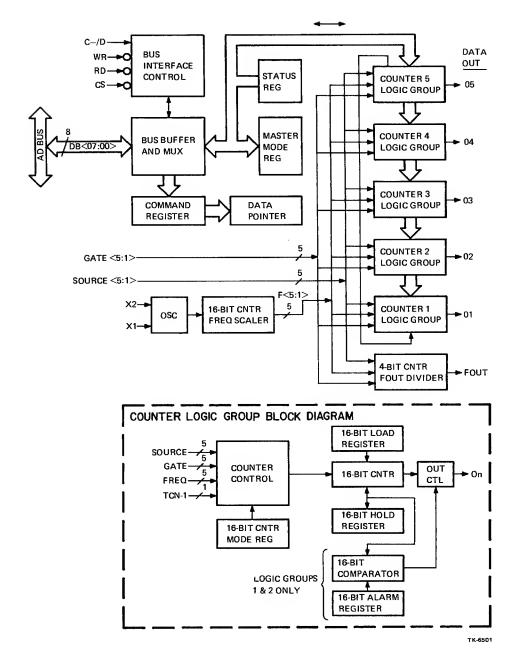

| 2-10                     | 9513 Internal Timer Block Diagram                                        |            |

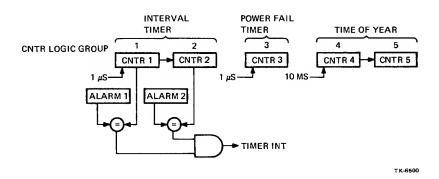

| 2-10                     | Utilization of 9513 Counter Logic Groups                                 |            |

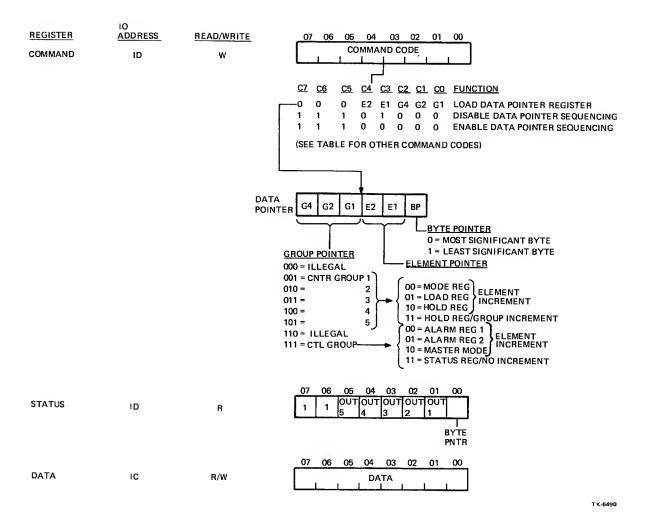

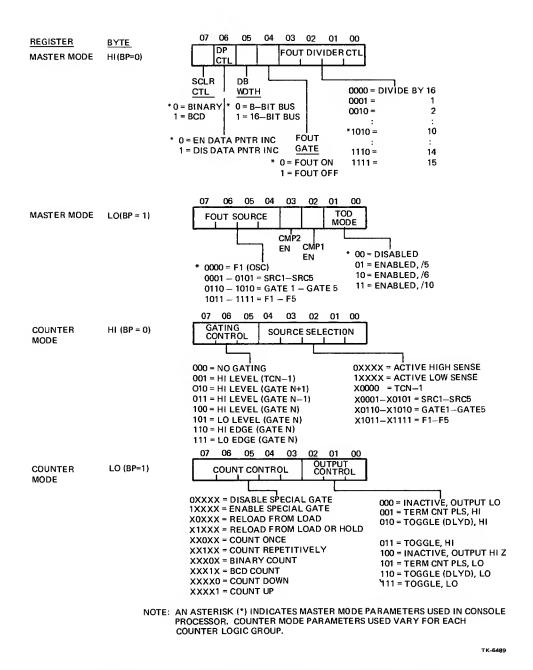

| 2-12                     | Bit Formats for 9513 Interval Timer Registers                            |            |

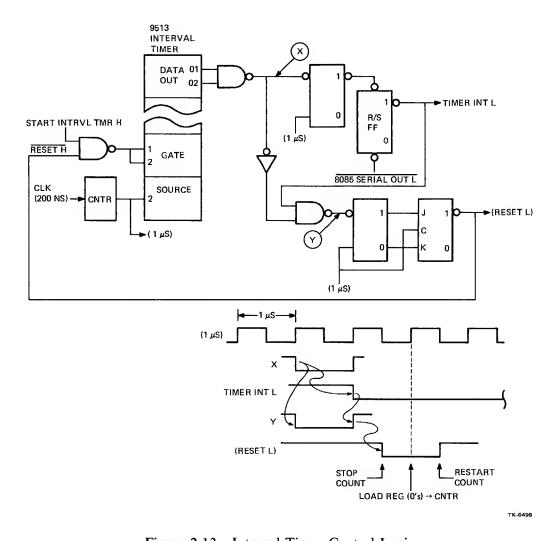

| 2-13                     | Interval Timer Control Logic.                                            |            |

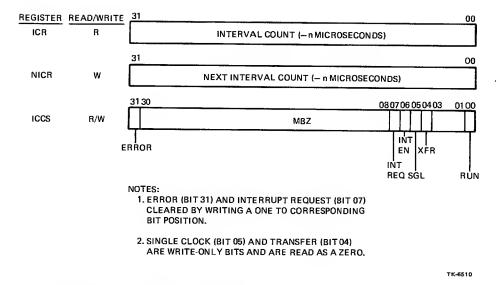

| 2-14                     | Bit Formats for Interval Timer Control Registers                         |            |

| 2-15                     | Time of Year Register Bit Format                                         |            |

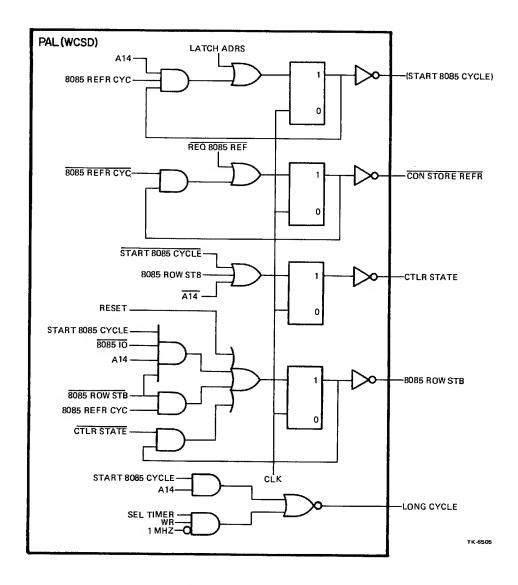

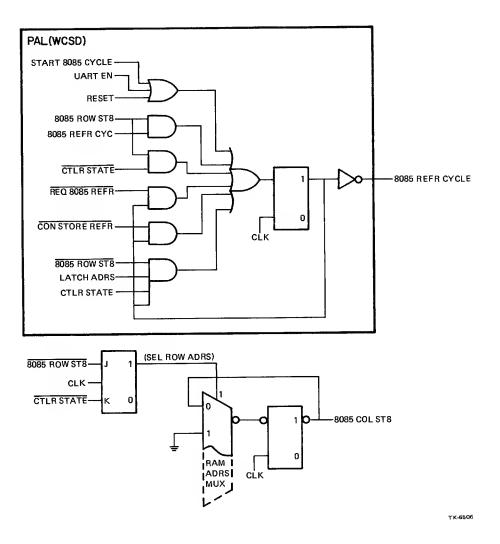

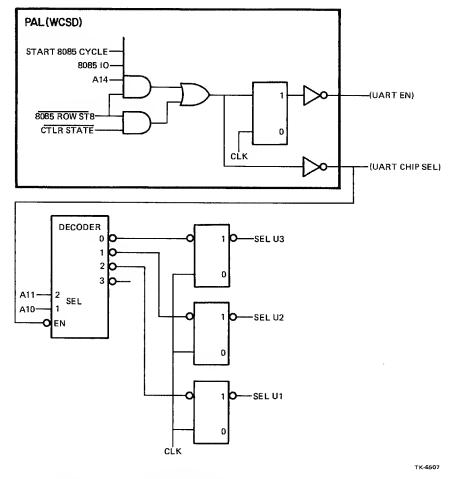

| 2-16                     | RAM/USART Control Logic.                                                 |            |

| 2-17                     | 8085A ROM Read Operation Timing Diagram                                  |            |

| 2-18                     | 8085A RAM Read/Write Operations Timing Diagram                           |            |

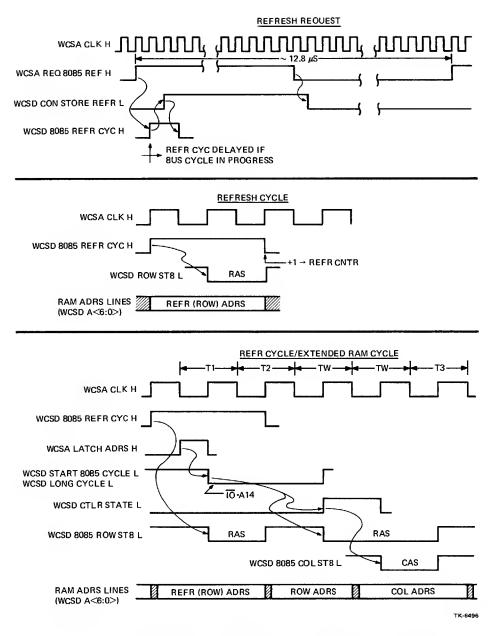

| 2-19                     | 8085A RAM Refresh Operation Timing Diagram                               |            |

|                          |                                                                          |            |

| 8085A I/O Space                                            | 2-40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

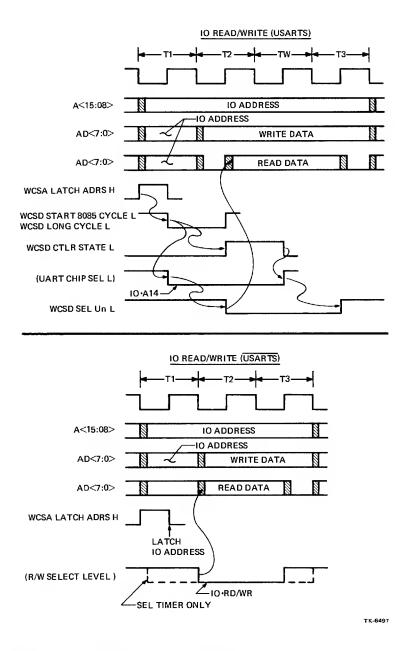

| 8085A I/O Read/Write Operations Timing Diagram             | 2-43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

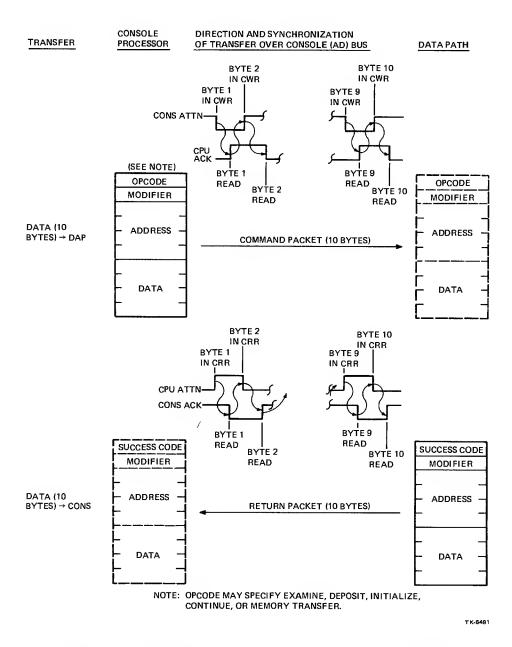

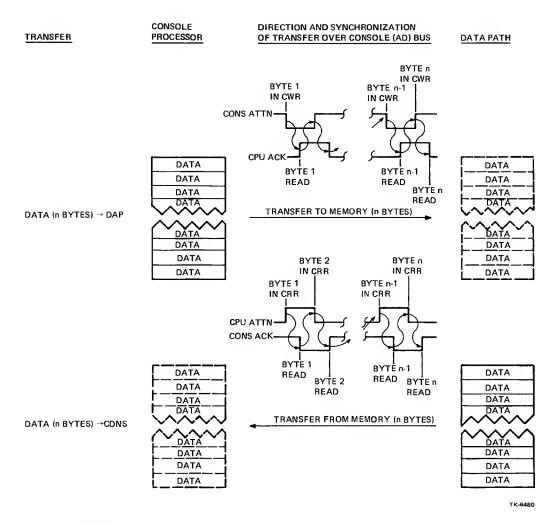

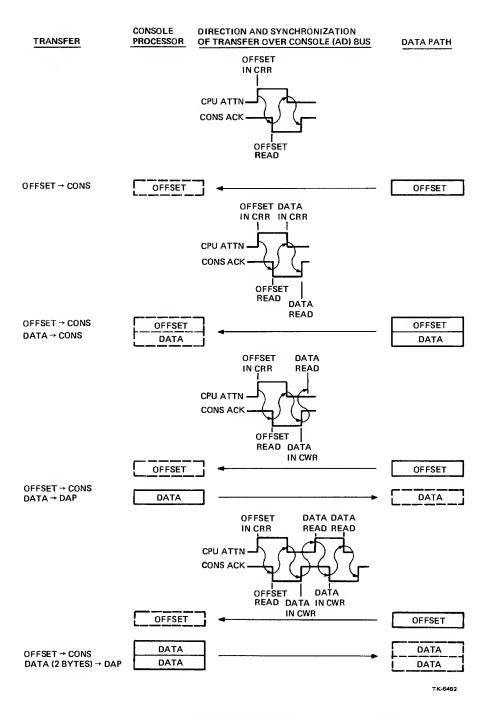

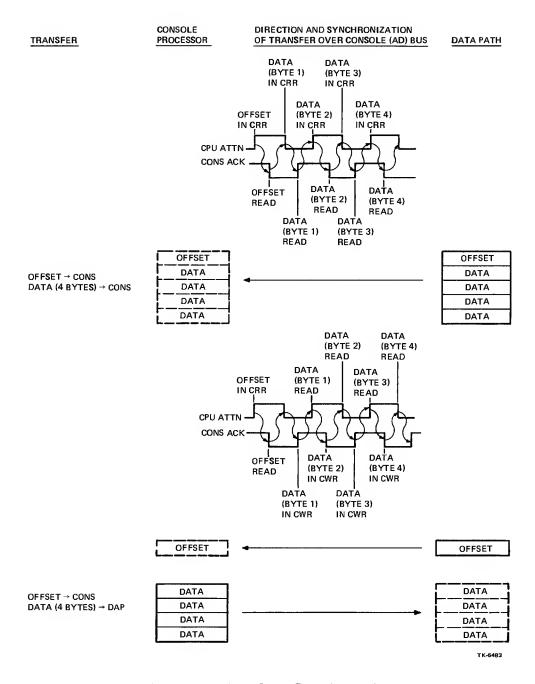

| Communications Over Console Bus in Console Mode            | 2-46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Communications Over Console Bus in Program Mode            | 2-49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

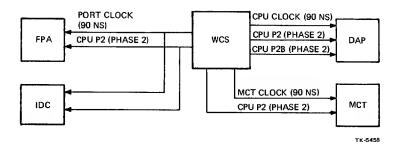

| Clock Distribution.                                        | 3-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

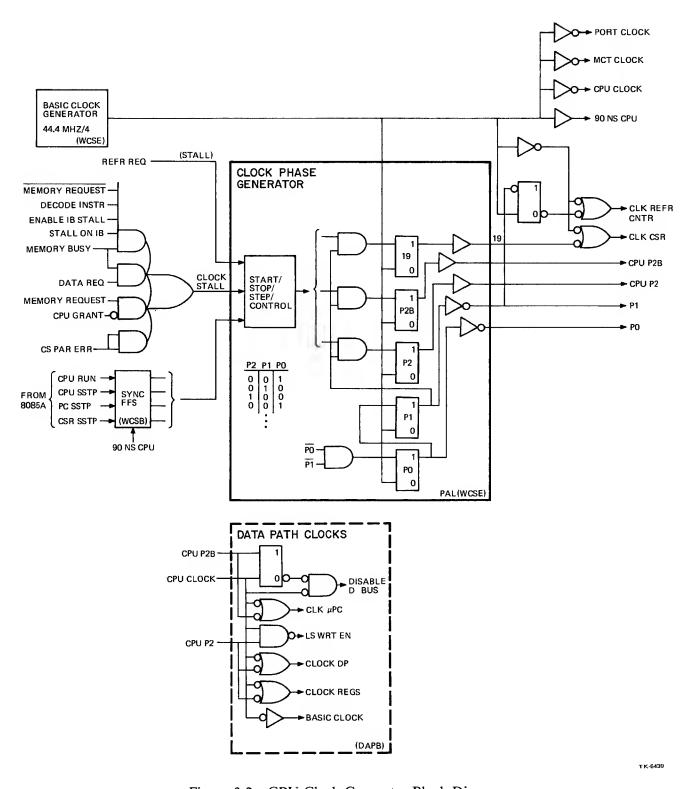

| CPU Clock Generator Block Diagram                          | 3-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

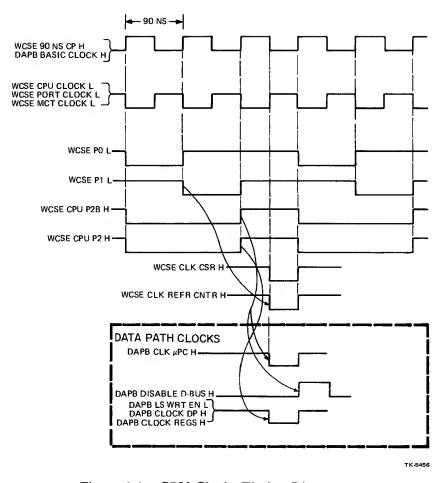

| CPU Clocks Timing Diagram                                  | 3-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Bit Formats for CPU Microinstructions                      | 4-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

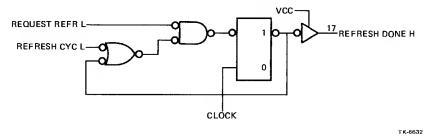

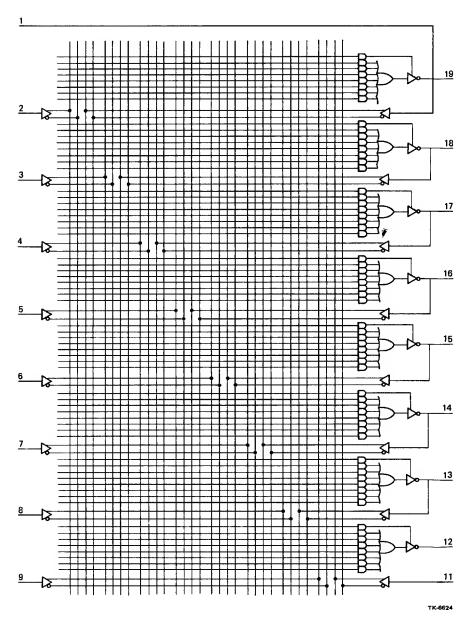

| Control Store Block Diagram                                | 4-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Basic Microcycle Timing Diagram                            | 4-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

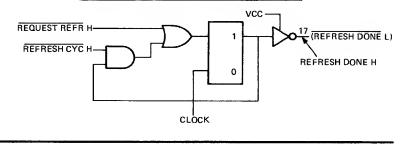

| Control Store Timing Circuit (Simplified)                  | 4-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

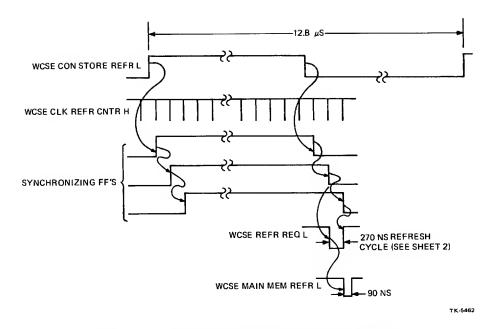

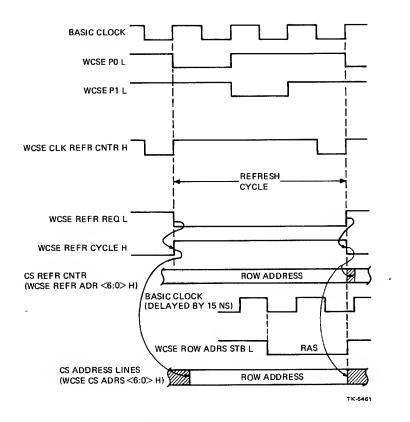

| Control Store Refresh Operation Timing Diagram             | 4-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

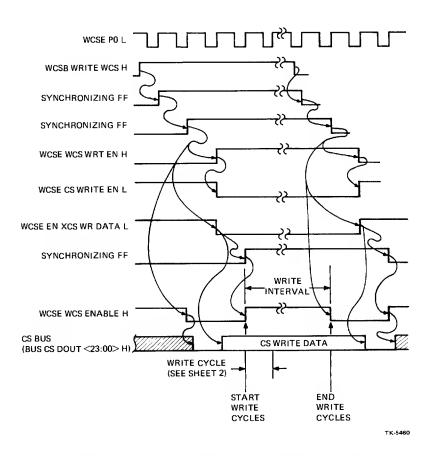

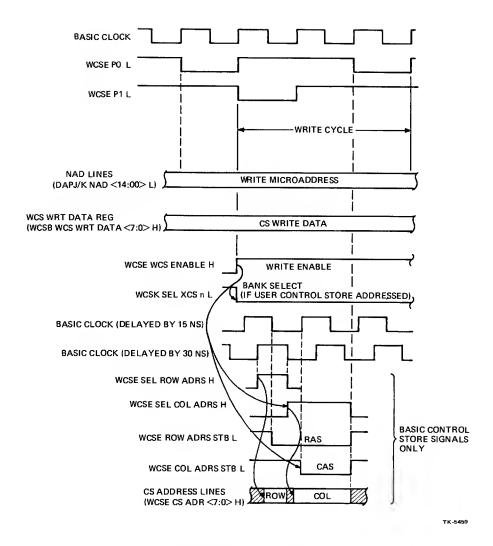

| Control Store Write Operation Timing Diagram               | 4-17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Microsequencer Block Diagram                               | 4-20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Subroutine Stack Addressing                                | 4-21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Skip (Or No-Skip) Timing Diagram                           | 4-25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Jump (Or No-Jump) Timing Diagram                           | 4-26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

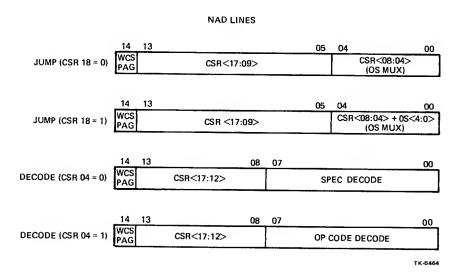

| Jump Address Selection                                     | 4-27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

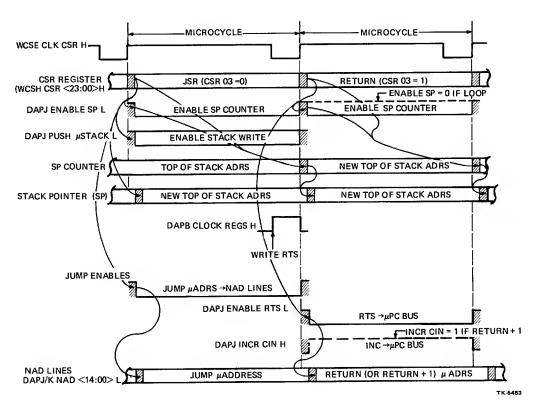

| ISR/Return Timing Diagram                                  | 4-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

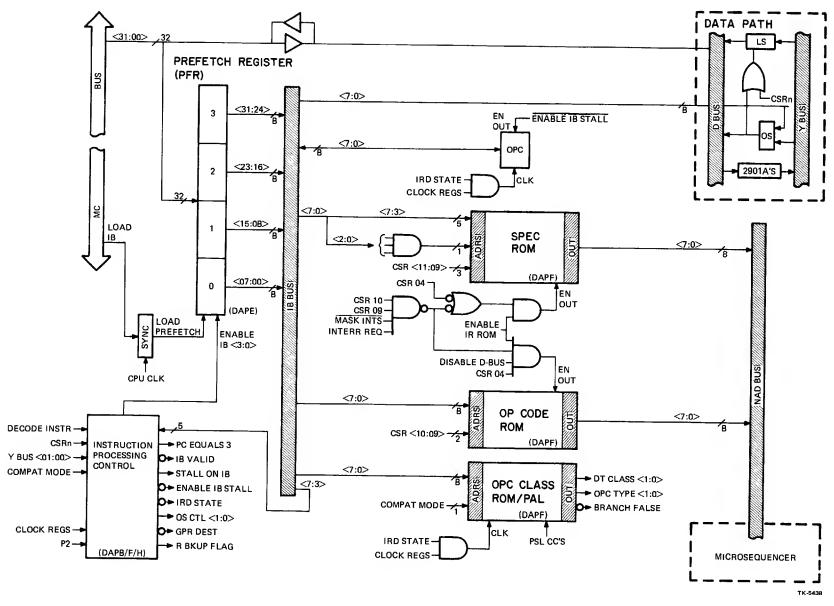

| Instruction Processing Hardware Block Diagram              | 5-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

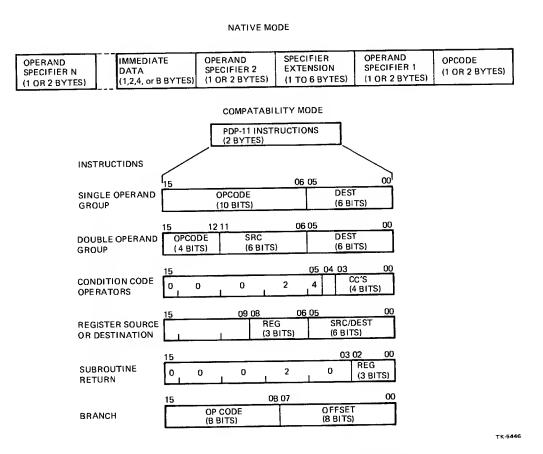

| Rasic Instruction Formats (Native and Compatibility Modes) | 5-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

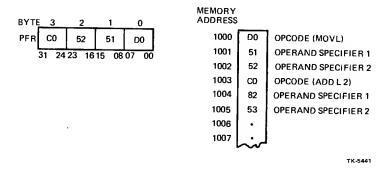

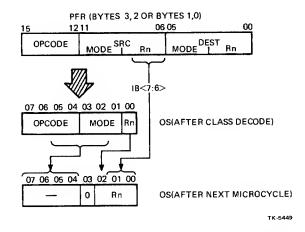

| Instruction Data in Memory and PFR                         | 5-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

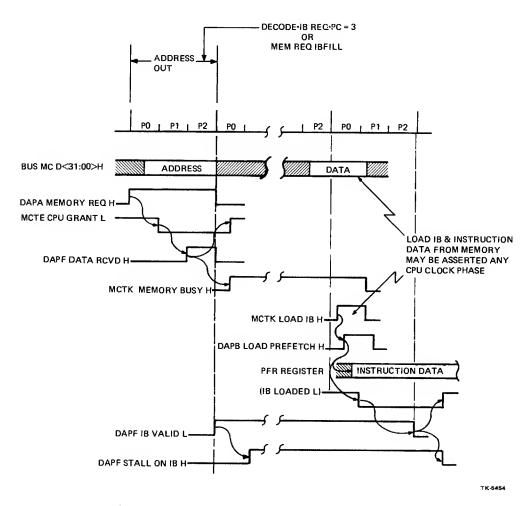

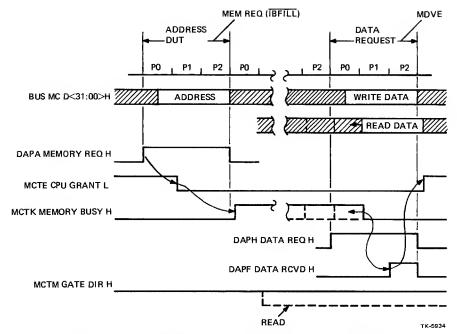

| PFR Load Operation Timing Diagram                          | 5-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

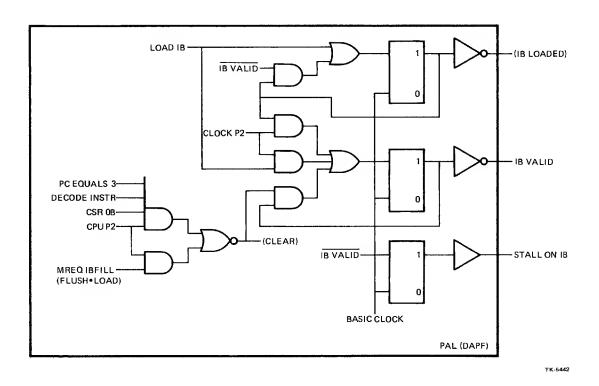

| IR VALID Control Logic                                     | 5-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

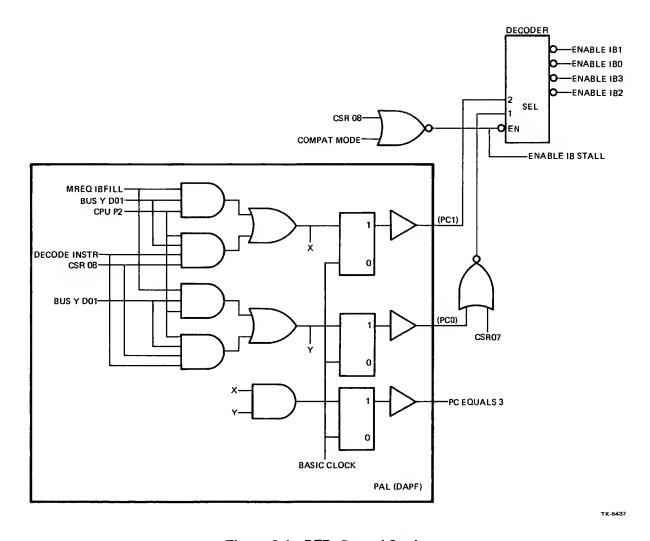

| PFR Control Logic                                          | 5-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

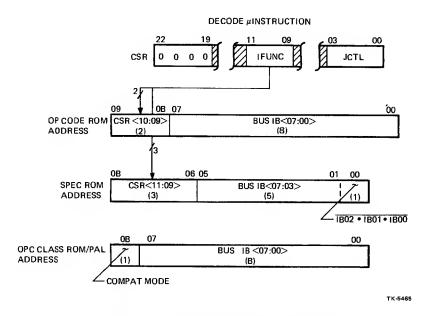

| Manning ROM Addressing                                     | 5-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| OPCODE ROM                                                 | 5-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SPEC ROM                                                   | 5-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

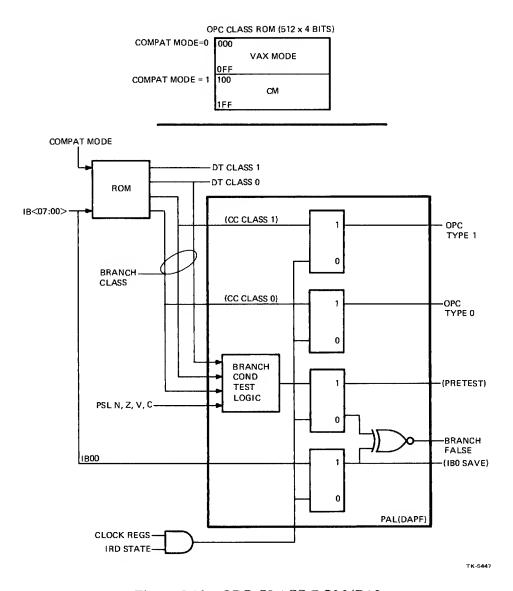

| OPC CLASS ROM/PAL                                          | 5-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

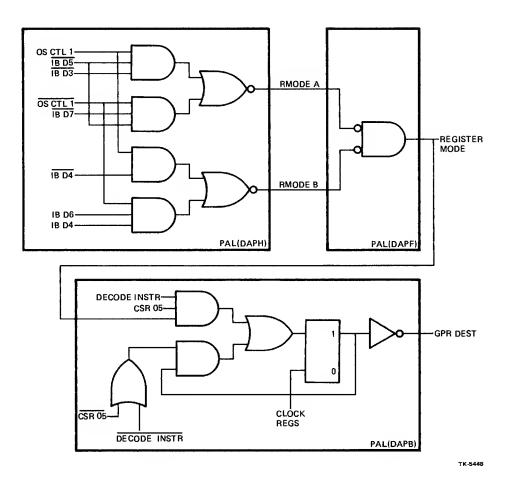

| GPR DEST Control Logic                                     | 5-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

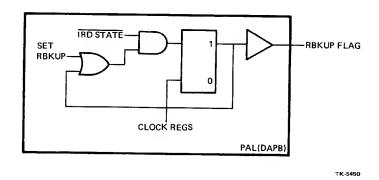

| RRKIIP FLAG Control Logic                                  | 5-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

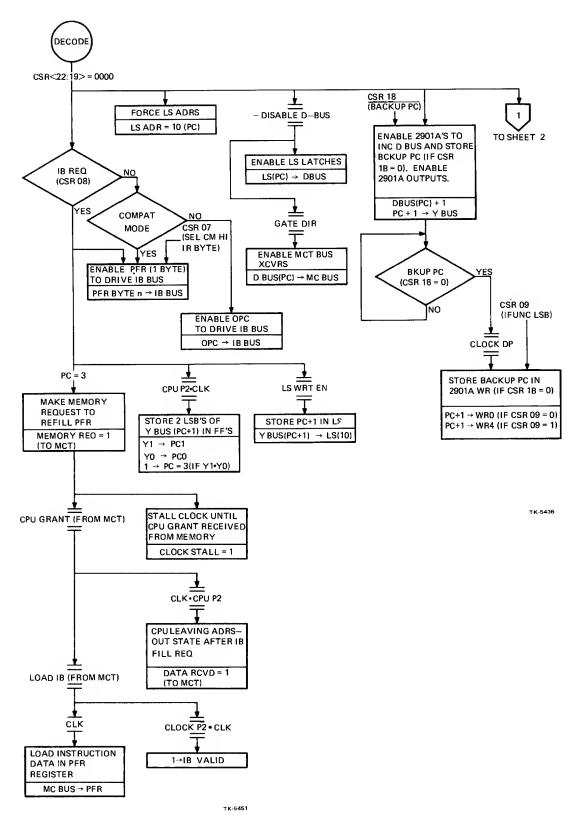

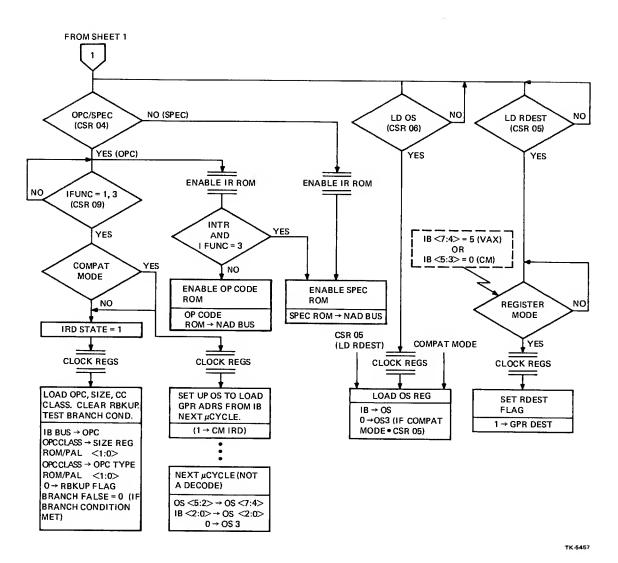

| DECODE Microinstruction Flow Diagram                       | 5-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Assembly of GPR Number in OS Following Class Decode in     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Compatibility Mode                                         | 5-19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

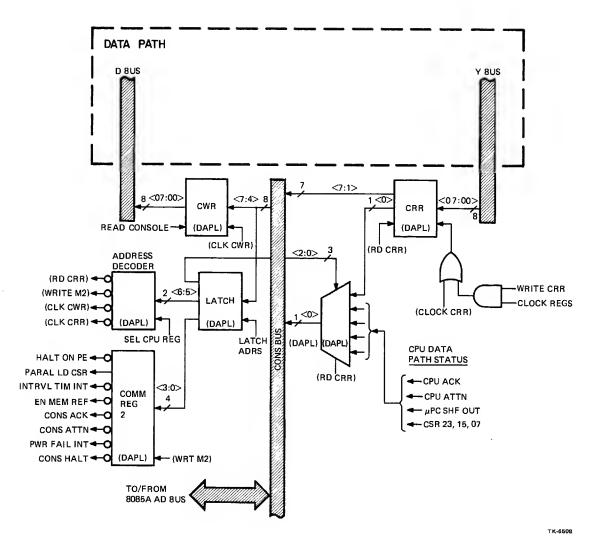

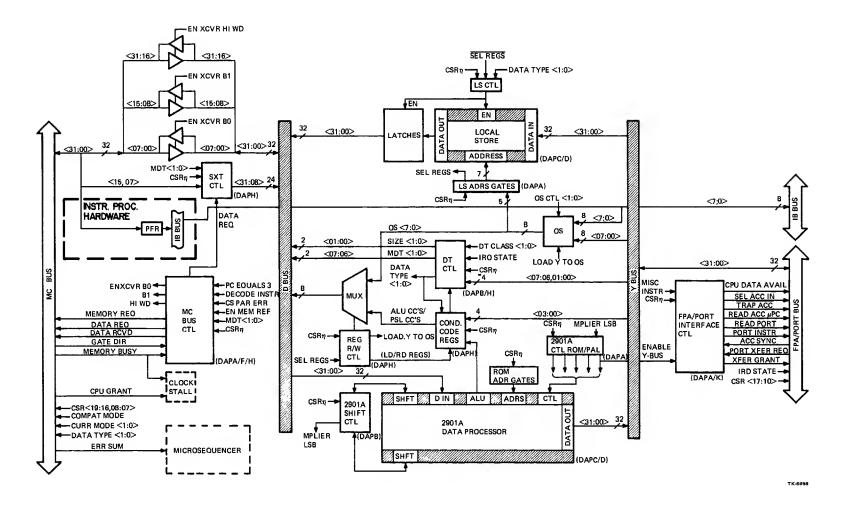

| Data Path Block Diagram                                    | 6-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Basic CPU Data Transfers                                   | 6-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Basic Data Path Timing                                     | 6-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2901 A Microprocessor Slice – Detailed Block Diagram       | 6-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Data Processor (Eight 2901As) Simplified Block Diagram     | 6-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |